Address, data in and other control signals are associated with the clock signals. Synchronous – all timings are initiated by the clock edges.Examples include the ubiquitous 28-pin 8K × 8 and 32K × 8 chips (often but not always named something along the lines of 6264 and 62C256 respectively), as well as similar products up to 16 Mbit per chip. Asynchronous – independent of clock frequency data in and data out are controlled by address transition.MOSFET (used in CMOS) – low power and very common today.

Bipolar junction transistor (used in TTL and ECL) – very fast but with high power consumption.It appears externally as slower SRAM, albeit with a density/cost advantage over true SRAM, and without the access complexity of DRAM. Pseudostatic RAM (PSRAM) has a DRAM storage core, combined with a self refresh circuit. nvSRAMs are used in a wide range of situations – networking, aerospace, and medical, among many others – where the preservation of data is critical and where batteries are impractical. Non-volatile SRAM (nvSRAM) has standard SRAM functionality, but they save the data when the power supply is lost, ensuring preservation of critical information. In synchronous SRAM, Clock (CLK) is also included. In addition to buses and power connections, SRAM usually requires only three controls: Chip Enable (CE), Write Enable (WE) and Output Enable (OE). It is much easier to work with than DRAM as there are no refresh cycles and the address and data buses are often directly accessible. Hobbyists, specifically home-built processor enthusiasts, often prefer SRAM due to the ease of interfacing. SRAM was used for the main memory of most early personal computers such as the ZX80, TRS-80 Model 100 and Commodore VIC-20. LCD screens and printers also normally employ SRAM to hold the image displayed (or to be printed). SRAM is also used in personal computers, workstations, routers and peripheral equipment: CPU register files, internal CPU caches and external burst mode SRAM caches, hard disk buffers, router buffers, etc. SRAM in its dual-ported form is sometimes used for real-time digital signal processing circuits. that implement an electronic user interface. Some amount (kilobytes or less) is also embedded in practically all modern appliances, toys, etc. Many categories of industrial and scientific subsystems, automotive electronics, and similar embedded systems, contain SRAM which, in this context, may be referred to as ESRAM. Applications and uses Ĭomparison image of 180 nanometre SRAM cells on a STM32F103VGT6 microcontroller as seen by an optical microscope Embedded use

The power consumption of SRAM varies widely depending on how frequently it is accessed.

Since SRAM requires more transistors per bit to implement, it is less dense and more expensive than DRAM and also has a higher power consumption during read or write access.

Performance and reliability are good and power consumption is low when idle. SRAM offers a simple data access model and does not require a refresh circuit. Though it can be characterized as volatile memory, SRAM exhibits data remanence. In 1965, Benjamin Agusta and his team at IBM created a 16-bit silicon memory chip based on the Farber-Schlig cell, with 80 transistors, 64 resistors, and 4 diodes. They replaced the latch with two transistors and two resistors, a configuration that became known as the Farber-Schlig cell. In 1965, Arnold Farber and Eugene Schlig, working for IBM, created a hard-wired memory cell, using a transistor gate and tunnel diode latch.

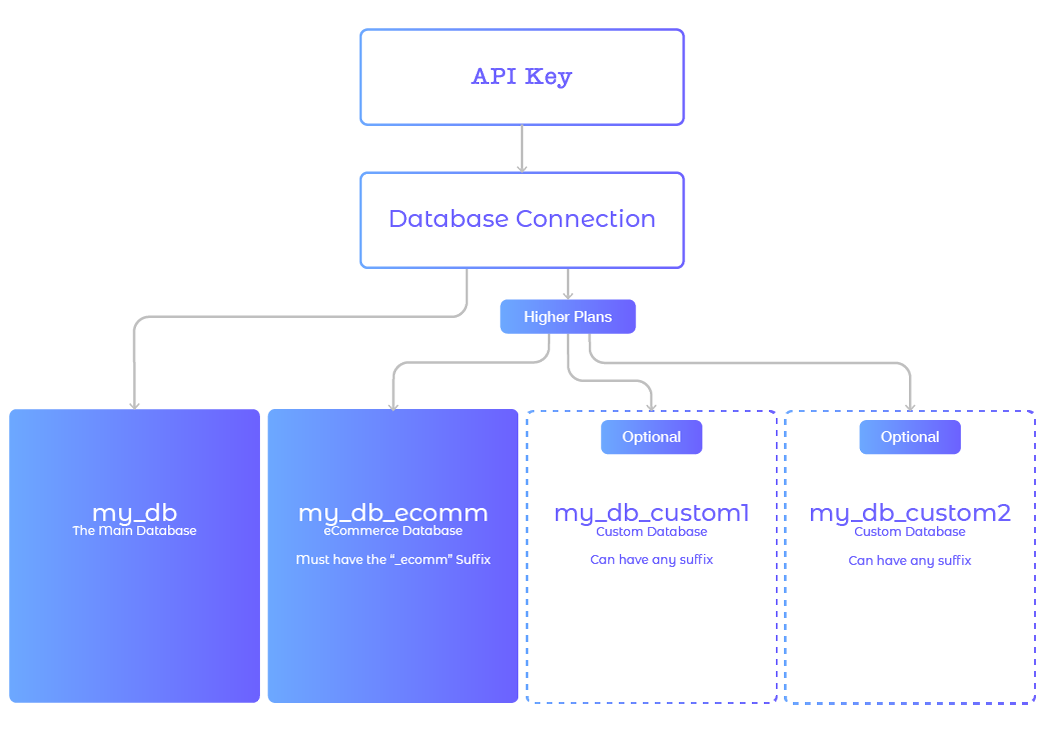

#Sqlectron database requirements driver#

The SRAM was the main driver behind any new CMOS-based technology fabrication process since 1959 when CMOS was invented. MOS SRAM was invented in 1964 by John Schmidt at Fairchild Semiconductor. Semiconductor bipolar SRAM was invented in 1963 by Robert Norman at Fairchild Semiconductor.

0 kommentar(er)

0 kommentar(er)